GitHub - coleblackman/TIDENet: TIDENet is an ASIC written in Verilog for Tiny Image Detection at Edge with neural networks (TIDENet) using DNNWeaver 2.0, the Google SkyWater PDK, OpenLANE, and Caravel.

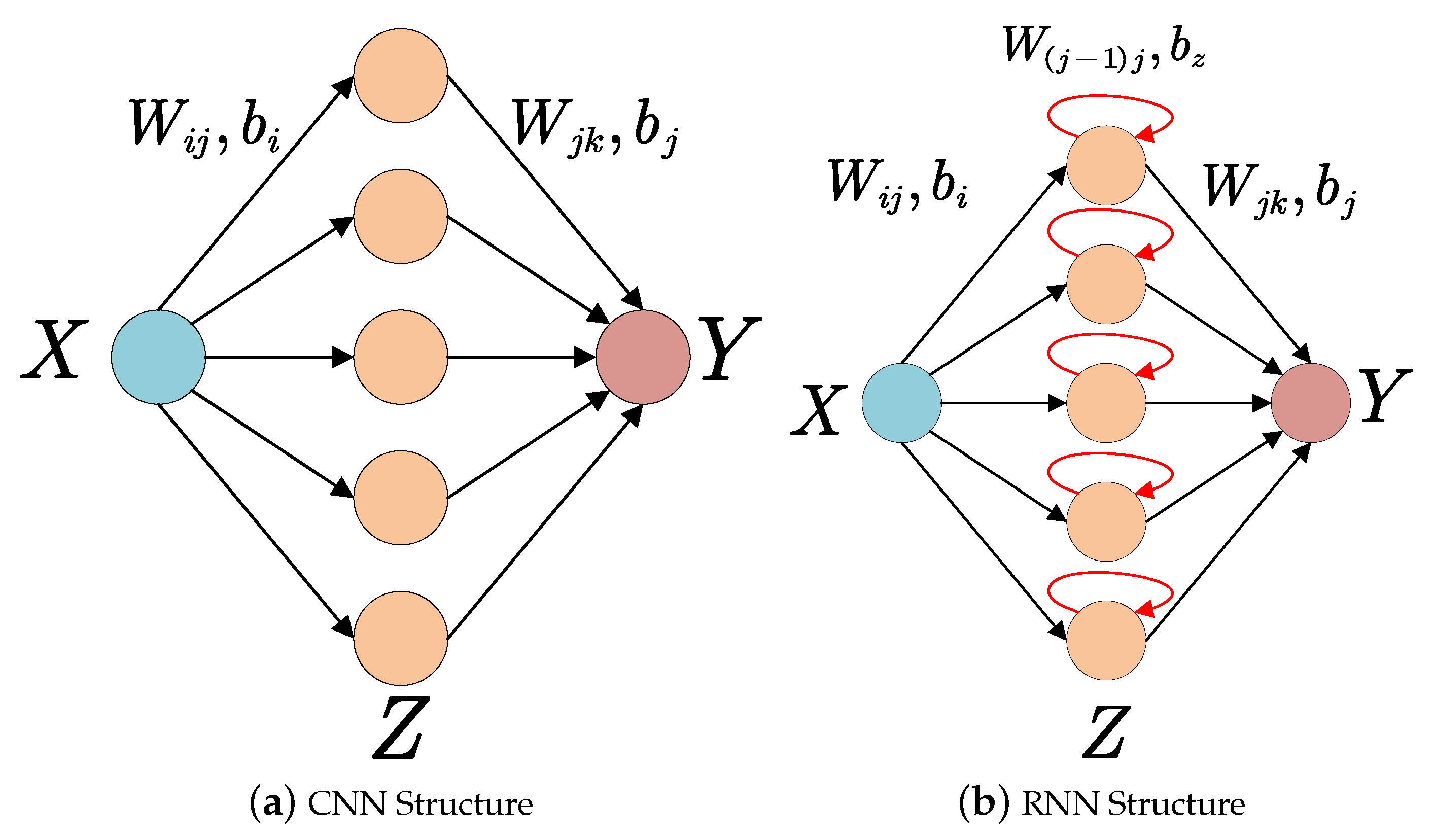

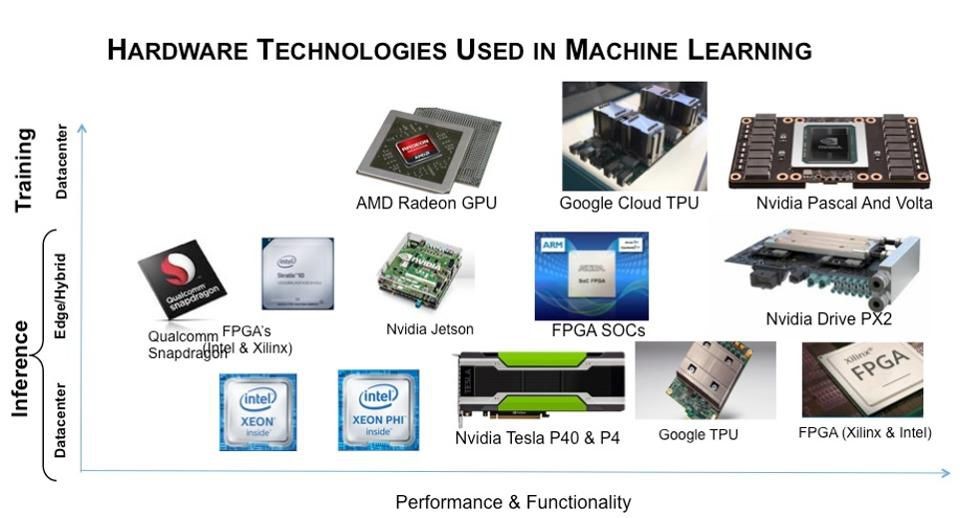

Electronics | Free Full-Text | Accelerating Neural Network Inference on FPGA-Based Platforms—A Survey

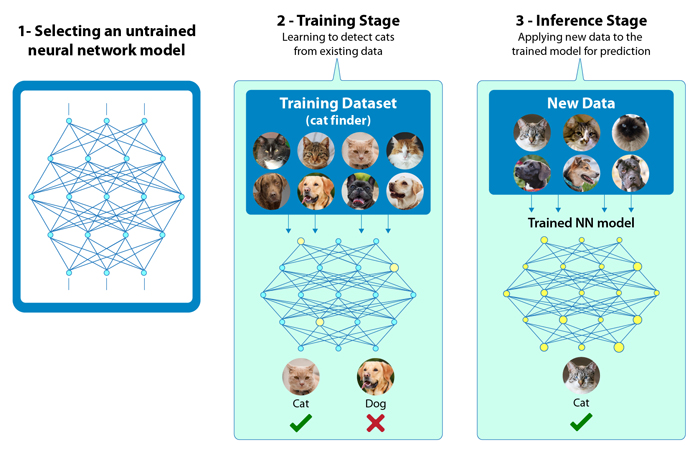

Machine Learning: How HLS Can Be Used to Quickly Create FPGA/ASIC HW for a Neural Network Inference Solution

![PDF] Accelerating Binarized Neural Networks: Comparison of FPGA, CPU, GPU, and ASIC | Semantic Scholar PDF] Accelerating Binarized Neural Networks: Comparison of FPGA, CPU, GPU, and ASIC | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/db4e71799cabeebf5530c26cccda0f8023c5af9f/3-Figure2-1.png)

PDF] Accelerating Binarized Neural Networks: Comparison of FPGA, CPU, GPU, and ASIC | Semantic Scholar

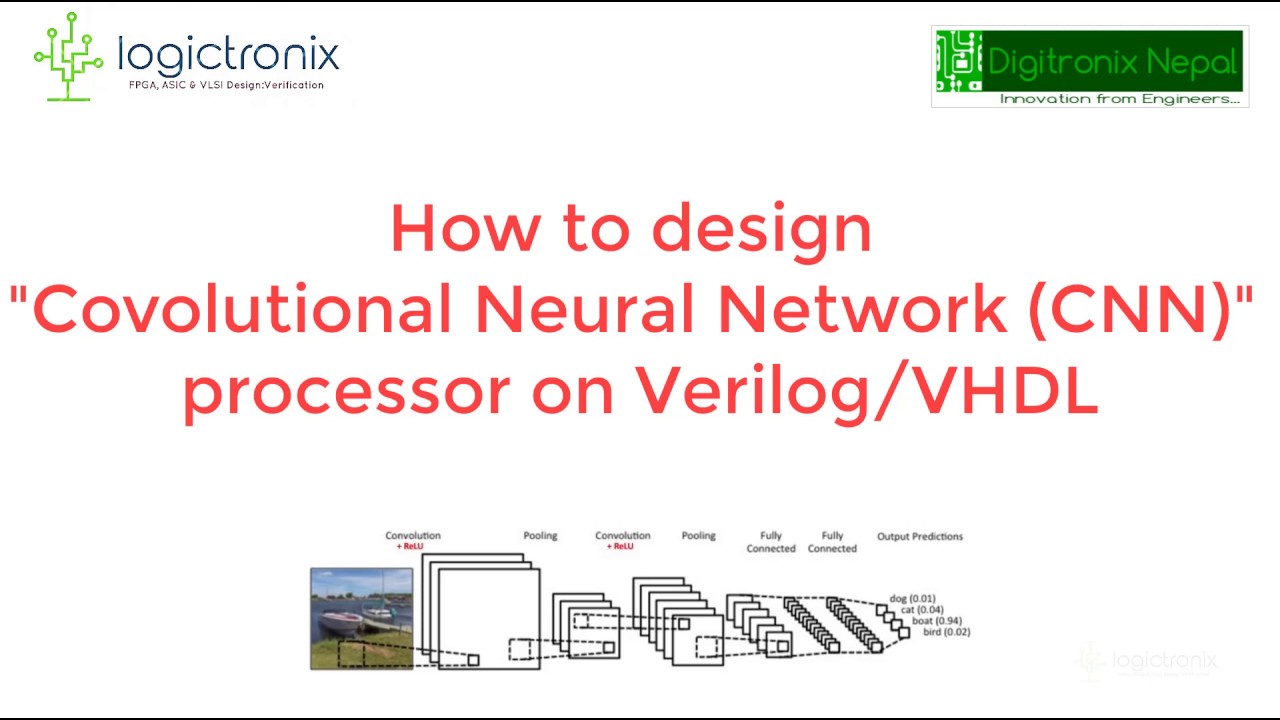

GitHub - zssloth/Embedded-Neural-Network: collection of works aiming at reducing model sizes or the ASIC/FPGA accelerator for machine learning

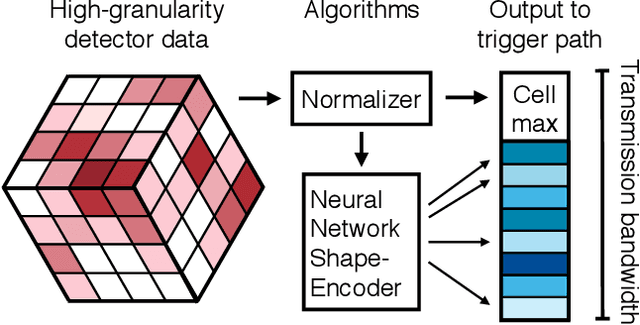

A reconfigurable neural network ASIC for detector front-end data compression at the HL-LHC - CERN Document Server

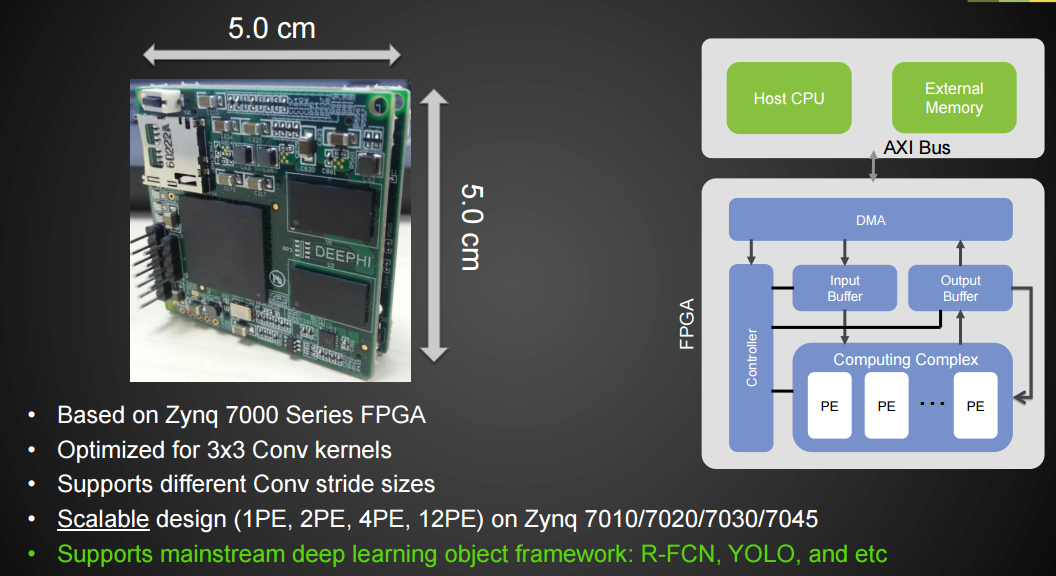

How to develop high-performance deep neural network object detection/recognition applications for FPGA-based edge devices - Blog - Company - Aldec

A reconfigurable neural network ASIC for detector front-end data compression at the HL-LHC: Paper and Code - CatalyzeX

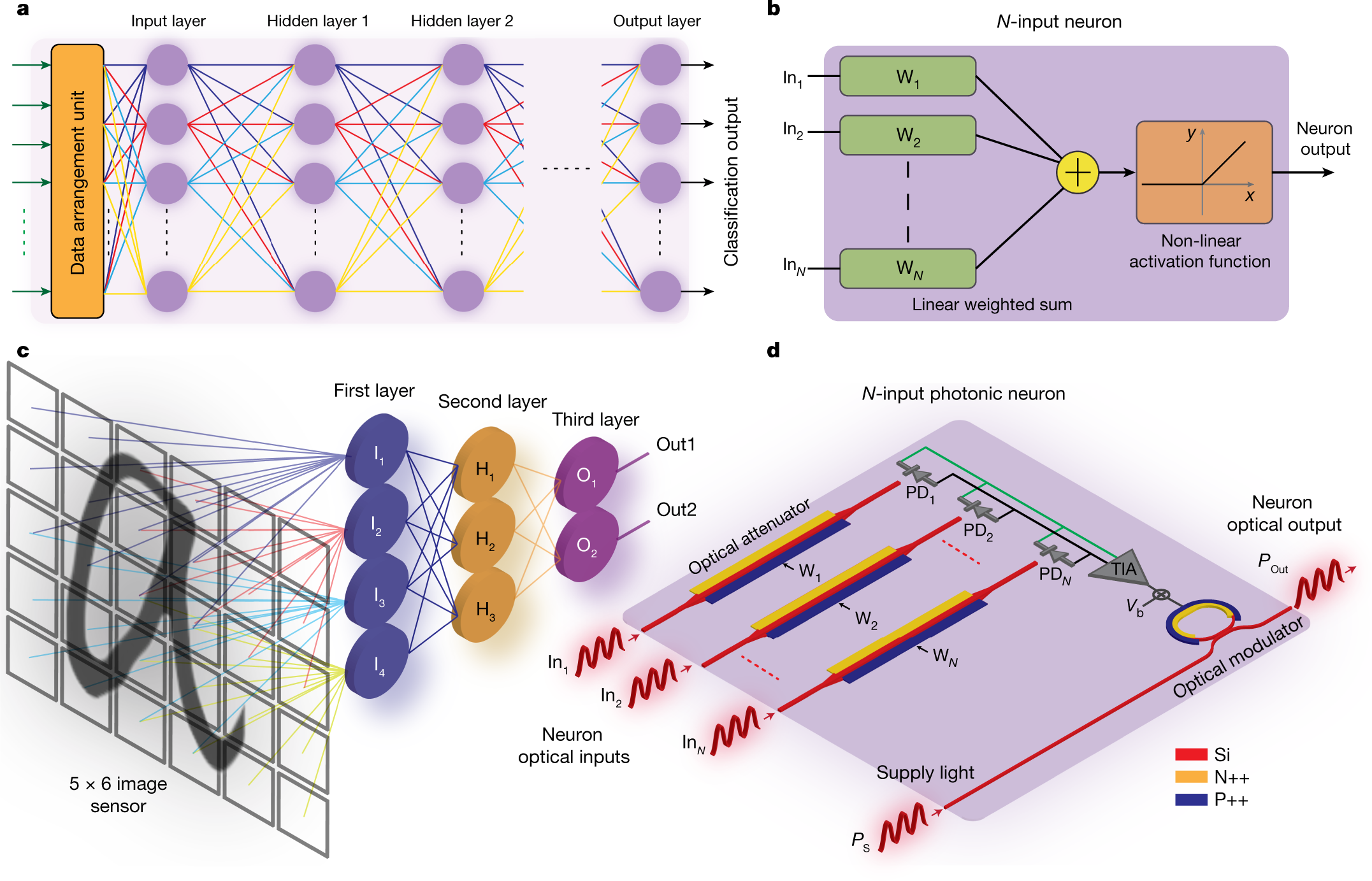

![PDF] ASIC Implementation of Neural Network Based Image Compression | Semantic Scholar PDF] ASIC Implementation of Neural Network Based Image Compression | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/2e6d769f42e3ccadefadb932337938f8a377d06c/1-Figure1-1.png)

![PDF] ASIC Implementation of Neural Network Based Image Compression | Semantic Scholar PDF] ASIC Implementation of Neural Network Based Image Compression | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/2e6d769f42e3ccadefadb932337938f8a377d06c/3-Figure4-1.png)